It is very difficult to run experiments to estimate such a low defect rate since the number of solder joints required is huge. Even larger sample sizes are required to reliably detect differences in defect rates corresponding to two experimental conditions (say, solder paste temperature A vs. solder paste temperature B) when the expected defect rates are so low. Therefore, some alternative characteristics that are likely to be correlated with the defect rate need to be investigated in addition to the actual defect rates.

One major component in the process is the volume of solder paste that is applied to bare ("dry") circuit board before surface mounting of the IC chips and discrete components. It is believed by the industry that larger variation in the solder paste volume should cause more defective joints. Thus, an important problem is to identify factors that contribute to the variation of the solder paste volume and to find operating conditions that give low variability. A large amount of solder volume data can be collected automatically by a computer vision system. A series of experiments was conducted in the Piscataway WTPC to achieve the following goals:

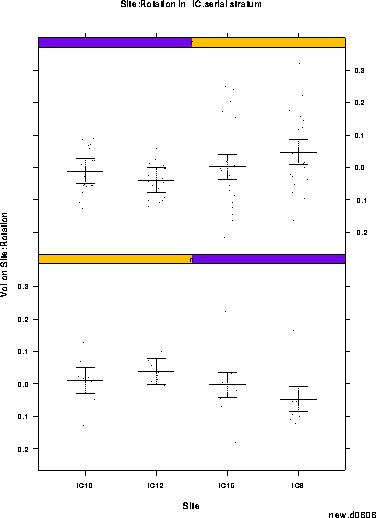

Here is an example of a trellis display of the interaction effect between factors IC Site and Printer Holder Rotation from the analysis of one printing experiment:

The plot shows that the influence of Site on solder paste Volume has different patterns as the Rotation of the holder changes.

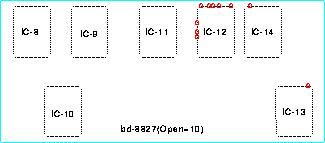

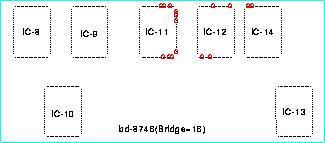

Another useful graphical method is to plot the location of the opens or bridges on all the ICs on each board. Here are two examples displaying open joints and bridges on a circuit board.

One important statistical issue is analyzing the temporal variation of the solder paste volume from board to board. The times since the last stencil wipe and the last addition of solder paste are very important factors influencing paste volume.

An experiment involving surface mount soldering of very small discrete components was run in Columbus in mid-1996. We analyzed the results and had been involved earlier in the design issues. The experiment identified certain pad shapes that are preferable and established dimensions and component spacing smaller than those currently in use for which the process can still perform reliably. The contact was Fred Verdi of ERC.

Back to the Statistics project page.

Back to the Statistics home page.

Last modified: $Date: 2000/11/02 21:14:29 $

dxsun@research.bell-labs.com